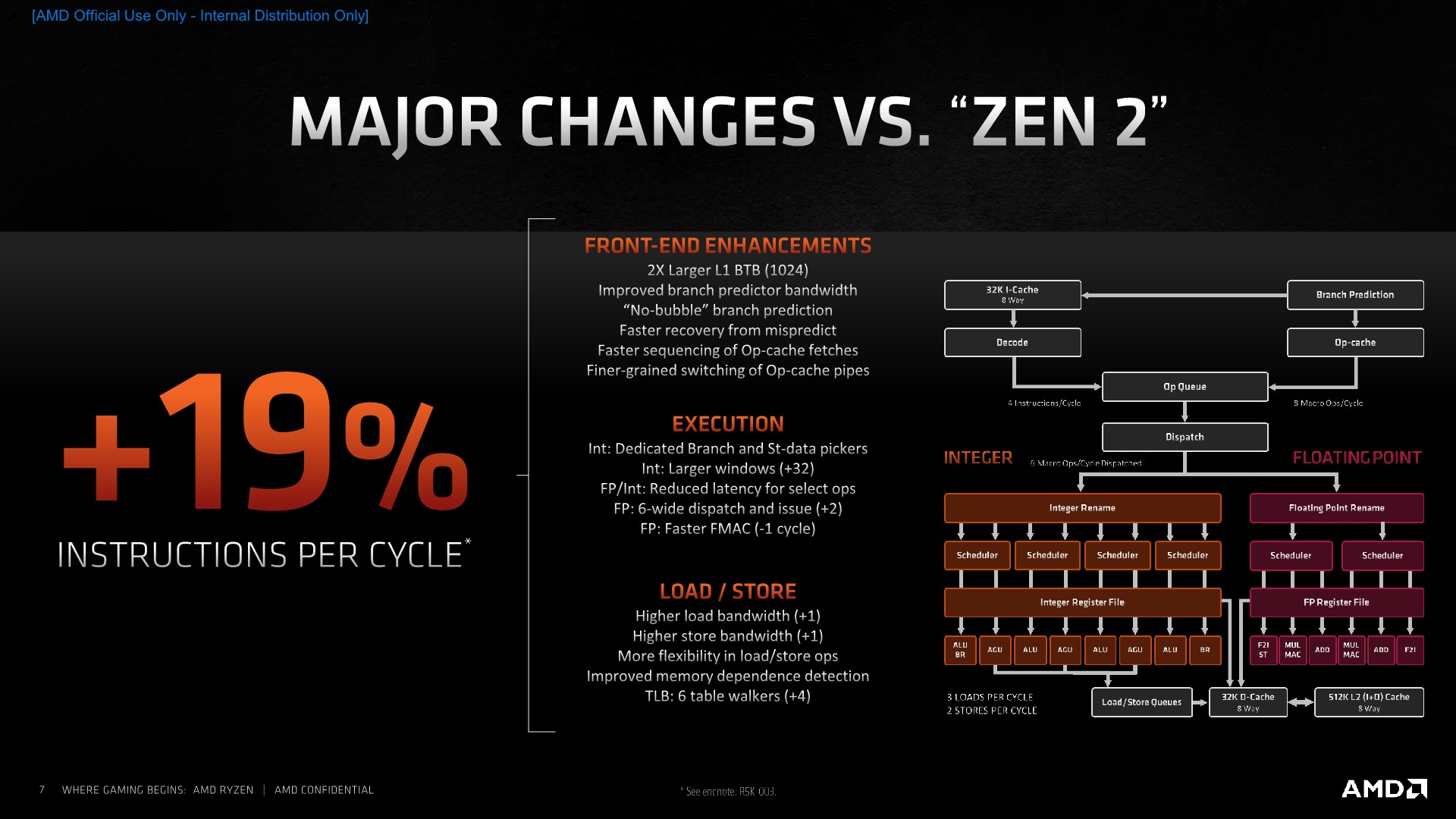

Furthermore, we updated our test system's drivers, benchmarking programs, and game clients to the latest versions at the time of testing. On the software front, we used a fresh 64-bit installation of Windows 10 Professional with all available updates. We updated the firmware for our Gigabyte B550 Aorus Master to the latest publicly-available revision. Windows 10 Professional 64-bit with October 2020 Update As usual, the trio needs to be on the same page for optimal operation, while breaking that synchronicity results in a heavy latency penalty that's detrimental to performance in some applications. The Infinity Fabric Clock (FCLK) continues to be in a permanent relationship with the unified memory controller clock (UCLK) and memory clock (MEMCLK) in a 1:1:1 ratio. That's an important consideration when selecting and tuning Ryzen's memory. On the memory front, Ryzen 5000 chips inherited the same I/O die and dual-channel memory controller as their predecessors, therefore, the mechanics remain unchanged. Ryzen 5000 wields AMD's latest Zen 3 cores that introduced important IPC gains, among other microarchitectural improvements. Four years later, AMD's foot is still on the pedal and taking the fight to Intel, with its latest army of Ryzen 5000 (codename Vermeer) processors leading the charge. After being off track for a few years, the chipmaker ultimately found the winning formula with its Zen microarchitecture. Basically you don't want your cores sitting idle so there is very little use for 's not always easy to stay on the right path, and AMD, like any other company, has had its ups and downs. In theory you could have 2 hosts fail and only then be at max CPU usage. That way you have leftover cycles if a host should fail.

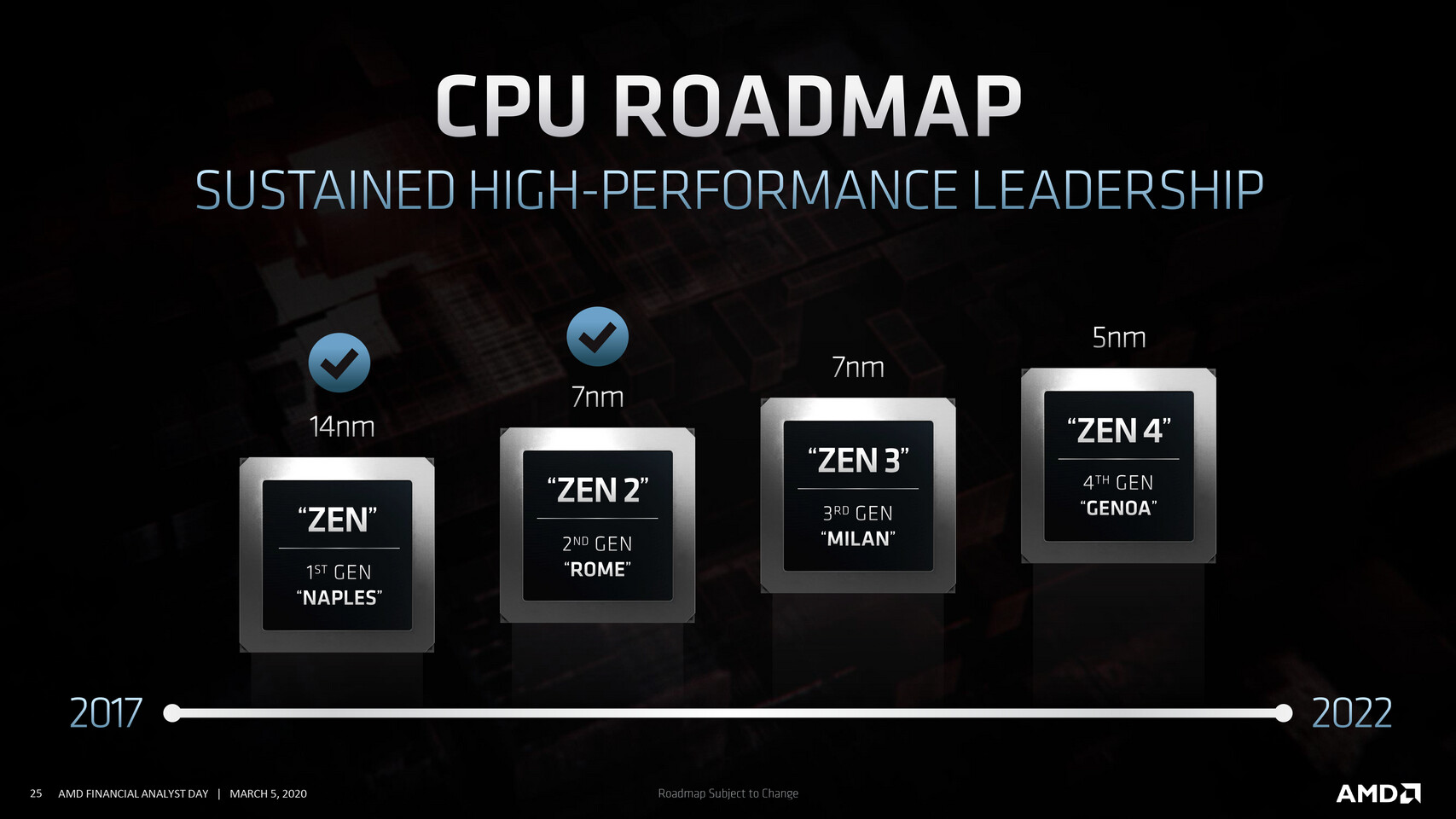

In an ideal scenario all your hosts will be running at 50% CPU capacity all the time. For example lets say you have a small 4 node datacenter. Due to virtualization you are always loading the cores and things that are mission critical need absolute best CPU performance. I would think that servers would also be a big beneficiary of efficiency cores given the electric-bill sensitivity of many data centers.Datacenter really won't benefit from big.LITTLE. Threadripper is aimed at a big core userbase that presumably wants max threads at all times and has the specialty software to leverage it. Having this many cores, it makes a lot of sense to have even 10 or so of them little efficiency cores. They have those Jaguar/Bobcat etc cores, it would be nice to see them used across the board for the low/mid end. Here's AMD's TLDR for the Zen 4 CPU roadmap:Įzst036 said:I want to see AMD adopt a big.LITTLE strategy in the future. In addition, Bergamo comes with a new type of 'Zen 4c' core optimized for specific use cases, meaning that AMD's Zen 4 chips will come with two types of cores, with the 'c' cores obviously being the smaller variants. The 96-core Genoa will come on the 5nm process in 2022, while the 128-core Bergamo, also on 5nm, will come to market in 2023. The new roadmap covers the fourth-gen EYPC processors. AMD also shared its first details of the 5nm TSMC process it will use for the new Genoa and Bergamo chips, claiming it provides twice the density and power efficiency along with 1.25X more performance than the 7nm process AMD uses for its current-gen chips. That adds yet more excitement to the event after AMD unveiled the EPYC Milan-X chips with up to 768MB of 元 cache and the Instinct MI250X GPU. AMD CEO Lisa Su shared the company's Zen 4 CPU roadmap today at its AMD Accelerated Data Center event, including a 96-core Genoa model and a 128-core Bergamo chip.

0 Comments

Leave a Reply. |

Details

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed